More than a decade ago, the frequency control industry introduced a phase-locked loop (PLL)-based oscillator, a pioneering innovation that uses many of the features not found in traditional crystal oscillators (XOs). With internal clock synthesizer IC technology, PLL-based XO is programmable to support a wider frequency range. This breakthrough eliminates the material processing steps required to cut and process quartz for resonance at a specific frequency. This innovation also makes frequency programming of PLL-based XO possible and enables extremely short lead times.

Given that traditional oscillator delivery cycles can be close to 14 weeks or longer, many hardware designers are eager to take advantage of programmable oscillators to achieve significant lead times. Unfortunately, serious problems have occurred. Some designs that have migrated from traditional XO to PLL-based XO fall into the context of jitter-related problems, which can cause associated applications (applicaTIon-related) failures involving ultra-high bit error rates ranging from communication links. To the inoperable SoC and processor. These problems have forced many IC vendors to specify that PLL-based oscillators cannot be used with their devices. This change in the situation has made hardware engineers who want to gain frequency flexibility and short lead times advantages through PLL-based oscillators.

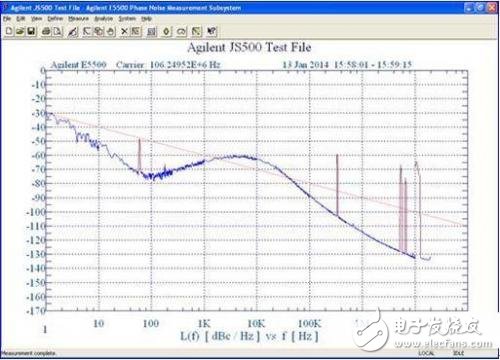

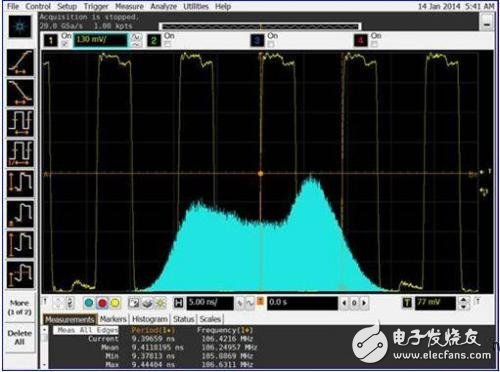

Why does this happen? The reason is that PLL technology from different vendors is extremely different. Unqualified PLL designs result in excessive oscillator phase noise and jitter peaks, as shown in the left panel of Figure 1. This particular PLL-based XO has a phase jitter of 150 ps RMS over a 12 kHz to 20 MHz bandwidth. This level of performance makes it unsuitable for clocking high-speed PHYs, which typically require a reference clock of 1 ps RMS jitter. The period jitter of the XO is shown in the picture on the right side of Figure 1. This bimodal period jitter can be a signal for PLL stability issues, and PLL stability can have detrimental performance effects on SoCs that use this XO. The second area related to the programmable oscillator exhibiting jitter peaks is the cascaded PLL. When such a PLL-based oscillator is connected to an IC with a PLL in a subsequent circuit, jitter may increase.

Figure 1 – Unqualified PLL-based XO design results in excessive phase noise and period jitter

The good news is that not all PLLs, not all PLL-based oscillators, are the same. With its unique PLL design technology, programmable oscillators provide jitter performance comparable to that of state-of-the-art quartz oscillators while overcoming the problems associated with cascaded PLLs. These high-performance PLL-based oscillators can be used for processor/SoC clocks, as well as high-speed serializers, PHYs, and FPGA clocks.

Developers can use three simple criteria to evaluate whether a PLL-based XO can be used for a given application.

Jitter Generation—In cascaded PLL applications (such as FPGA and PHY clocks), XO reference clock jitter is mixed with FPGA/PHY internal PLL jitter. Using a low-jitter XO reference clock (such as "1ps RMS Phase Jitter" maximizes the jitter value produced by the permissible FPGA/PHY internal PLL, maximizing the jitter margin of the overall design.

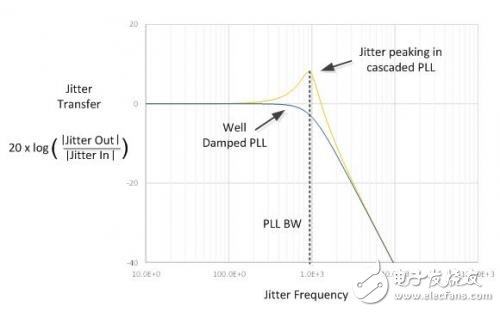

Jitter Peak—The cascaded PLL is at risk of excessive jitter when the loop bandwidths of the first and second stage PLLs are the same. This risk is easily mitigated by using a PLL-based oscillator with a relatively low internal PLL bandwidth. The PLL should be well suppressed to ensure that it does not exceed 1% of the peak ("0.1db"), as shown in Figure 2. Universal soc" 1MHz. Using a PLL-based oscillator with low jitter peaks and very low internal bandwidth ensures that its peak does not overlap with the bandwidth of the downstream PLL. This architecture allows the second stage PLL to easily track changes in the first stage PLL while maintaining acceptable loop stability and phase margin.

Figure 2 - PLL-based jitter tracking and filtering helps mitigate jitter peaks

Phase Noise - How do you know if a PLL-based oscillator is right for your application? It is easier to observe the oscillator's period jitter using an oscilloscope. The oscillator phase noise measurement is performed using a spectrum analyzer. If you don't have a spectrum analyzer, contact your frequency control provider for phase noise measurements. Phase noise can be calculated directly from the phase noise plot by applying the required jitter synthesis bandwidth required. The phase noise chart also shows the spurious performance of the reference clock. Spurious signals superimposed on phase jitter can be easily measured to ensure that application requirements are met. The phase noise chart also shows any peak effects of the internal PLL. An overdamped PLL will exhibit low peaks.

Silicon Labs offers an easy-to-use online jitter calculator that converts phase noise into jitter. Simply input the carrier frequency and its associated phase noise signature data, and the tool can calculate the final phase jitter, period jitter, and inter-cycle jitter of the clock. Web-based tools are available on the Silicon Labs website.

In summary, today's programmable oscillators offer excellent frequency flexibility, short-term, and reliable lead times. However, the difference in PLL performance provided by programmable oscillators from different vendors can be quite large. For high performance applications including FPGA transceivers and Ethernet PHY clocks, programmable oscillators can be easily evaluated by comparing the jitter parameters in the data sheet specifications.

In an ASIC, SoC, FPGA, or PHY application with an internal PLL driven by an oscillator, it is important to ensure that the combination of the reference oscillator and the SoC does not produce jitter peaks. Jitter peaks are usually not listed in the oscillator data sheet. A simple solution is to perform phase noise measurements on the oscillator. This phase noise distribution will show any peak effects on the internal PLL and can be easily converted to equivalent clock jitter performance.

Disposable vape pen Onlyrelx 600puffs is portable and fashion disposable electronic cigarette, disposable ecigs pen are trending featured vape pen for vapors as it's safety and easy to use. Disposable vape pod,disposable vape, wholesale vape,vape wholesale,vape pen manufacturer and supplier.disposable vape pen,disposable electronic cigarette,disposable ecigs pen,disposable ecigs stick,disposable e-cigs pen,disposable vape factory,disposable vape pod,disposable vape device,vape pen,vape stick, vape wholesale,wholesale vape,customized dispsoable vape pen,customized vape pen,OEM&ODM disposable ecigs pen,disposable electronic cigarette wholesale, wholesale disposable electronic cigarette,distribute vape pen,vape pen distribute,high quality vape pen,high quality vape pod,rechargeable disposable vape pen,refillable vape pen,refilling electronic cigarette,rechargeable disposable electronic cigarette,refillable vape pod,disposable refillable ecigs,disposable refilling e-cigs pen,refillable e-cigs pen

Onlyrelx Bar600,Onlyrelx flat shape bar,Mini Vaporizer Onlyrelx,Original Onlyrelx Vape Pen,disposable vape pen,disposable vapes pen

Shenzhen Onlyrelx Technology Co.,Ltd , https://www.onlyrelxtech.com