Digital filtering is a fundamental technique in applications such as spectrum, speech, and image processing. Compared to analog filtering, digital filtering has many outstanding advantages. Digital filtering can meet the strict requirements of amplitude and phase in performance, which can avoid voltage drift, temperature drift and noise problems. It has the advantages of good stability, high precision and strong anti-interference ability [1].

Today's digital signal filtering is mostly implemented by a microprocessor ASIC (ApplicaTIon Specific Integrated Circuit) chip [2]. In recent years, with the rapid development of large-scale integrated circuit technology, DSP (Digital Signal Processor) technology and microprocessor technology are closely combined, which can greatly improve the computing speed and accuracy of the system, making a new generation of microprocessor with DSP core. Become the core component of high-end intelligent instruments and equipment. However, the price of a high-performance professional DSP chip is also expensive. In the system development, the overall cost price of the system must be considered, and a suitable design solution should be selected. DSP's ASIC filter chips are often used in specialized applications such as high-resolution measurements of DC voltage, temperature, pressure, and quality signal measurements. How to implement digital filtering at low cost becomes a challenge by using flexible design methods [3].

The seismic data acquisition system is an instrument for geological exploration. The vibration signal on the ground is converted into a digital form and recorded, and the structure of the stratum is obtained by inverting the collected data. This paper proposes and implements a design scheme combining FPGA (Field Programmable Gate Array) and MCU (Micro Control Unit) for the digital filtering design of seismic data acquisition system, taking into account development cost and flexibility. The idea of ​​the solution is not only applicable to seismic data acquisition systems, but also to various sensor networks such as voltage, pressure, and audio.

1 Digital filtering system structureIn the design of modern seismic data acquisition, in order to obtain high-resolution vibration signals, not only the data accuracy requirement is 24 bits, but the signal-to-noise ratio is usually better than 110dB when the system is tested [4]. Another feature of seismic data acquisition is that the effective energy is in the low frequency part [5], usually below a few hundred hertz, so only a data sampling rate of 1 kHz / s is required [6].

The Sigma-Delta converter oversamples the analog signal at much higher than the Nyquist sampling rate, making it ideal for high-accuracy A/D conversion of slowly varying signals with frequencies below a few kilohertz. The Sigma-Delta A/D converters currently widely used in seismic data acquisition mainly include Cirrus Logic's CS5371 /5372 high-precision 24-bit A/D converter [7].

According to the characteristics of seismic data acquisition Sigma-Delta high oversampling, a digital decimation filter needs to be designed at the back end to extract and condition the signal. There are three functions that need to be implemented: one is to reduce the high-speed signal frequency of the modulator output to the Nyquist frequency; the other is to filter out the high-frequency noise of the modulator output; and the third is to convert a digital signal output from the modulator. High-precision multi-bit digital output signal [8].

When digital filters are used in Sigma-Delta A/D converters, theoretically, they can be implemented using either FIR (Constant Impulse Response) digital filters or IIR (Infinite Impulse Response) digital filters. The IIR filter has an infinitely long impulse response, but the phase characteristics of the IIR digital filter are not well controlled. When the phase requirement is high, a phase calibration network is required, so the IIR digital filter is not suitable. The FIR filter has no feedback loop, so there is no instability problem and a strict linear phase can be achieved. Since the Sigma-Delta A/D converter is a high-precision, high-fidelity A/D converter, in addition to ensuring the accuracy of the signal amplitude, it must also ensure that the relative phase of each frequency component of the signal does not change, otherwise it will Phase distortion [9].

The high oversampling of the Sigma-Delta A/D converter requires a high decimation rate for the digital decimation filter, and the filter can achieve higher efficiency with a multi-stage decimation structure. Compared with the single-stage structure, the multi-level extraction structure requires less computation and storage, and the normalized bandwidth of each stage is wider, which can reduce the finite word length effect [8]. In addition, since the data rate is reduced when the decimation method is applied, the clock rate required for the subsequent operation of the FIR filter is also reduced, and the power consumption in the high-speed hardware system can be minimized.

The structure of a direct FIR filter requires many multipliers and adders. Such a structure requires more area and cost, so it is necessary to reduce the use of multipliers and adders. CIC Filter (Cascaded Integrator - Comb Filter) is a high-efficiency calculation for narrow-band low-pass filter. Its frequency response curve is similar to SINC function sin( x) /x. It is usually applied in modern communication systems for hardware extraction. And interpolation. An important feature of CIC filters that are popular in hardware design is that they do not require multiplication, only add and subtract, which can reduce computational complexity and facilitate system implementation [10].

In CIC filter decimation/interpolation applications, it is often desirable to have a flat passband and a narrow transition band, but this is not consistent with the characteristics of the CIC filter itself. To solve this problem, the CIC filter The front-end or back-end typically have a high-performance linear phase low-pass FIR filter whose task is to compensate for the non-flat transmission band of the CIC filter.

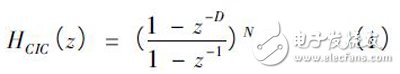

Figure 1(a) shows a classic first-order CIC filter consisting of a delay unit and an addition and subtraction unit. For a C-C filter with an N-order delay of D, the z-domain transfer function is:

LED Wall Wash Light

Wall Wash Light Series Include 36x12w LED Wash light, 19x15w Led wash light; Both is hot selling in the lighting market.

36X12W RGBW 4 IN 1/5 IN 1/6 IN 1 /LED Wash Moving Head Light

Specification:

Pure bright in color effect, excellent color mixing, good heat cooling

36 pcs 12W RGBWA+UV 6in1 LED, 36 pcs 10W RGBWA 5in1 LED, 36 pcs 10W RGBW 4in1 LED

10-60 zoom angle, narrow beam effect to wide wash effect, functional in usage.

Small size, easy to carry and install, each unit weighs only 9kg

Linear smooth dimmer from 0-100%, 1-20 times strobe per second, flicker-free for TV and films.

Suitable for mobile productions, events, parties, stage installations, theater, musical concert, TV studios.

Our company have 13 years experience of LED Display and Stage Lights , our company mainly produce Indoor Rental LED Display, Outdoor Rental LED Display, Transparent LED Display,Indoor Fixed Indoor LED Display, Outdoor Fixed LED Display, Poster LED Display , Dance LED Display ... In additional, we also produce stage lights, such as beam lights Series, moving head lights Series, LED Par Light Series and son on...

Wall Wash Light Series,Disco Light,Led Washer Light,Moving Head

Guangzhou Chengwen Photoelectric Technology co.,ltd , https://www.cwstagelight.com